# CSE 590: Special Topics Course (Supercomputing)

Lectures 7 & 8 (GPGPU Computing & CUDA)

Rezaul A. Chowdhury

Department of Computer Science

SUNY Stony Brook

Spring 2012

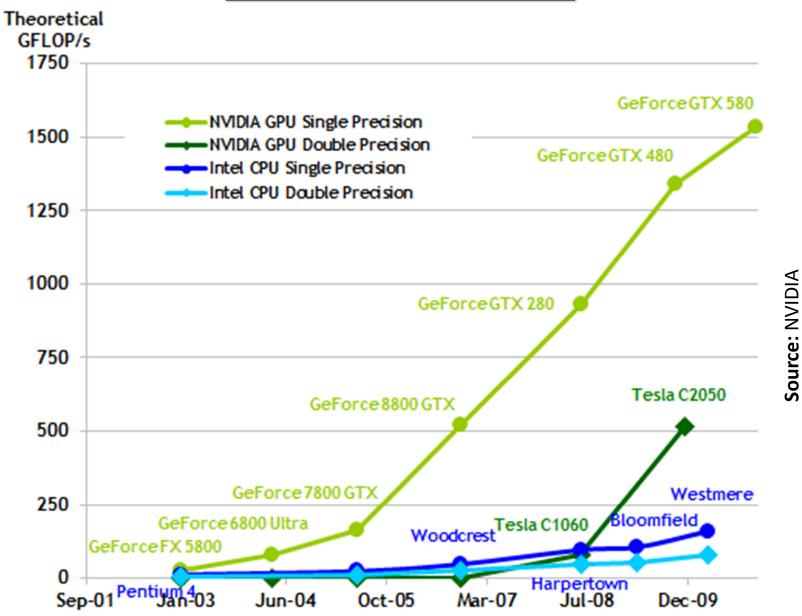

#### GPU vs CPU: FLOP/s

#### **GPU vs CPU: Memory Bandwidth**

Theoretical GB/s

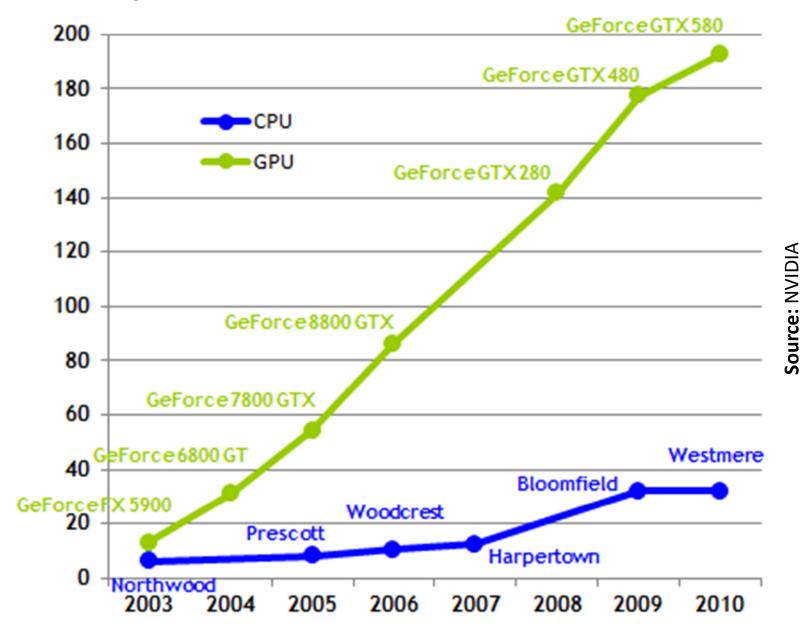

CPU's are designed for *general purpose computations* requiring sophisticated control flow and caching mechanisms.

GPU's are designed for *special purpose computations* with massive data-parallelism and high arithmetic intensity.

- Since the same program is executed for each data element there is a lower requirement sophisticated flow control

- Because of high arithmetic intensity, the memory access latency can be hidden with calculations instead of big caches

So GPU's can devote more transistors to data processing rather than data caching and flow control.

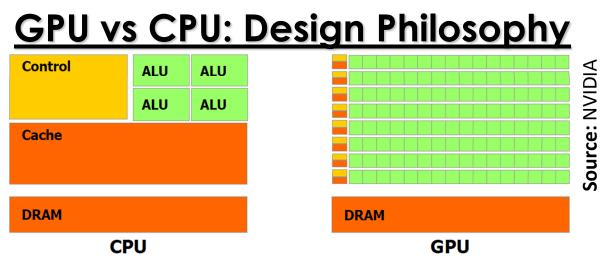

# **Architecture of a Modern GPU**

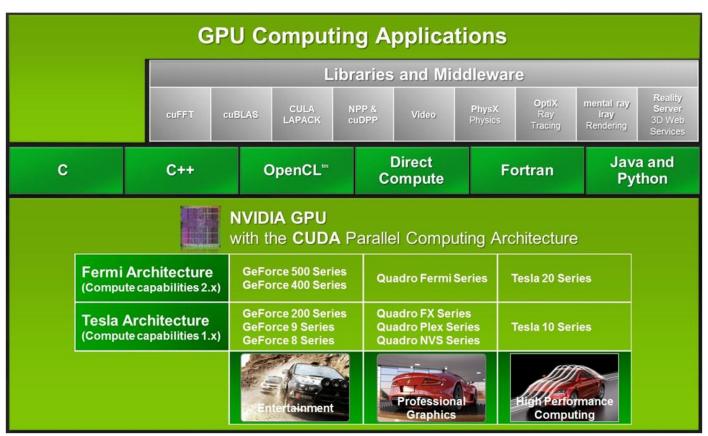

#### **CUDA (Compute Unified Device Architecture)**

A general purpose parallel computing architecture with

- a new parallel programming model, and

- instruction set architecture

that leverages the parallel compute engine in NVIDIA GPUs to solve data-parallel computations more efficiently than CPUs.

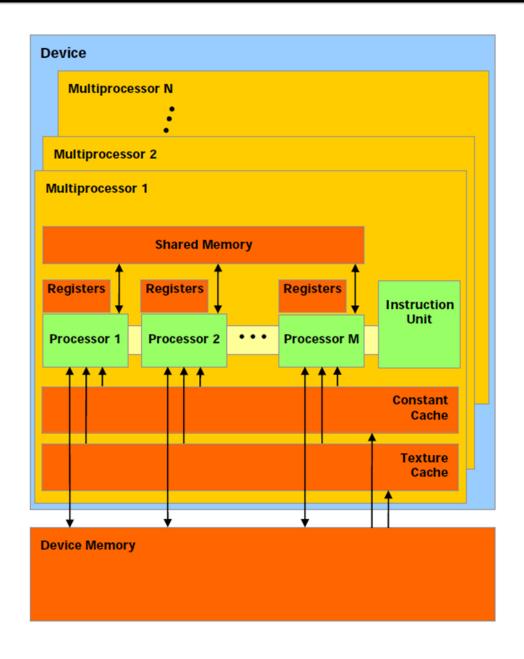

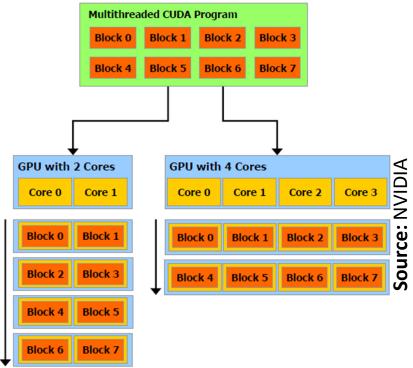

#### **CUDA: a Scalable Programming Model**

Three Key abstractions exposed as a minimal set of language extensions

- A hierarchy of thread groups

- Shared memories

- Barrier synchronization

The programmer partitions

- the problem into coarse subproblems that can be solved independently in parallel by blocks of threads

- each sub-problem into finer pieces that can be solved cooperatively in parallel by all threads within the block

The thread blocks can be executed in any order — concurrently or sequentially — leading to automatic scalability.

#### <u>Differences between CPU and CUDA Threads</u>

- CUDA threads are extremely lightweight compared to CPU threads

- Only a few cycles to create

- Instant switching

- CUDA runs thousands of threads while CPU's run only a few

# **CUDA Extensions to C Functional Declarations**

|                            | Executed on the: | Only callable from the: |

|----------------------------|------------------|-------------------------|

| device float DeviceFunc( ) | device           | device                  |

| global void KernelFunc( )  | device           | host                    |

| host float HostFunc( )     | host             | host                    |

#### **Kernel Functions**

- Called from host (CPU)

- Executed on device ( GPU )

- Only one kernel runs at a time (for compute capability < 2.0)</li>

- All running threads execute the same kernel (except above)

- All kernel launches are asynchronous (control returns to the CPU immediately)

#### **Kernel Functions (Restrictions)**

```

// Kernel definition

__global__ void VecAdd(float* A, float* B, float* C)

{

int i = threadIdx.x;

C[i] = A[i] + B[i];

}

int main()

{

...

// Kernel invocation with N threads

VecAdd<<<1, N>>>(A, B, C);

...

}

```

- Must return void

- Variable number of arguments (i.e., varargs) not allowed

- No static variables

- No access to host memory

- Must be non-recursive

#### **Thread Hierarchy: Thread Index**

Threads can be identified using a 1, 2 or 3 dimensional thread index forming a 1, 2 or 3 dimensional thread block.

```

// Kernel definition

global void MatAdd(float A[N][N], float B[N][N],

float C[N][N])

int i = threadIdx.x;

int j = threadIdx.v;

C[i][j] = A[i][j] + B[i][j];

int main()

// Kernel invocation with one block of N * N * 1 threads

int numBlocks = 1;

dim3 threadsPerBlock(N, N);

MatAdd<<<numBlocks, threadsPerBlock>>>(A, B, C);

. . .

```

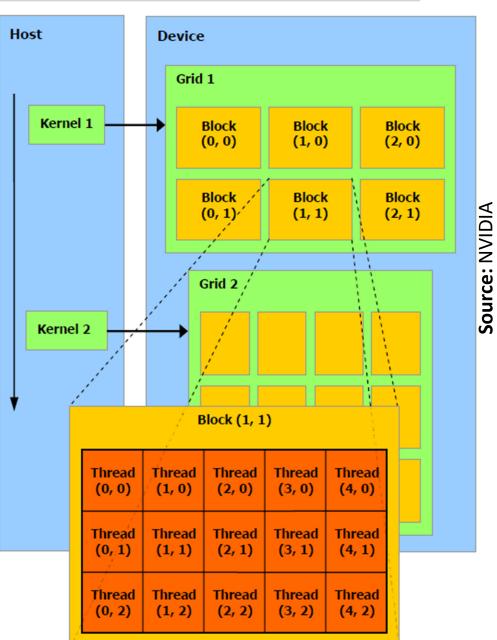

#### Thread Hierarchy: Block Index

Blocks can be identified using a 1, 2 or 3 dimensional *block index* forming a 1, 2 or 3 dimensional *grid*.

```

// Kernel definition

global void MatAdd(float A[N][N], float B[N][N],

float C[N][N])

int i = blockIdx.x * blockDim.x + threadIdx.x;

int j = blockIdx.y * blockDim.y + threadIdx.y;

if (i < N \&\& i < N)

C[i][j] = A[i][j] + B[i][j];

int main()

// Kernel invocation

dim3 threadsPerBlock(16, 16);

dim3 numBlocks(N / threadsPerBlock.x, N / threadsPerBlock.y);

MatAdd<<<numBlocks, threadsPerBlock>>>(A, B, C);

```

#### <u>Thread Hierarchy: Grids, Blocks and Threads</u>

All \_\_device\_\_ and \_\_global\_\_ functions have access to the following built-in device variables

- dim3 gridDim: dimenions of the grid in blocks

- dim3 blockDim: dimenions of a block in threads

- dim3 blockIdx: block index within the grid

- dim3 threadIdx: thread index within a block

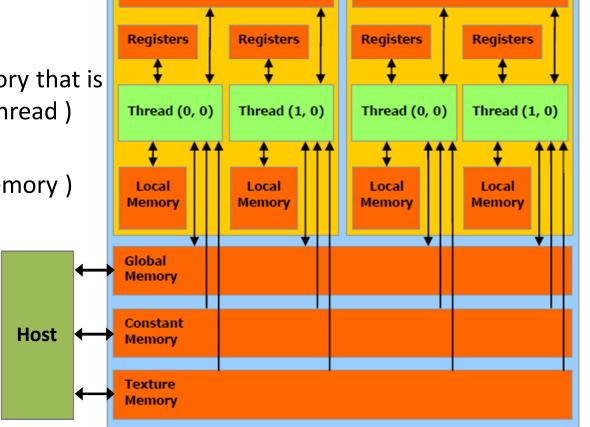

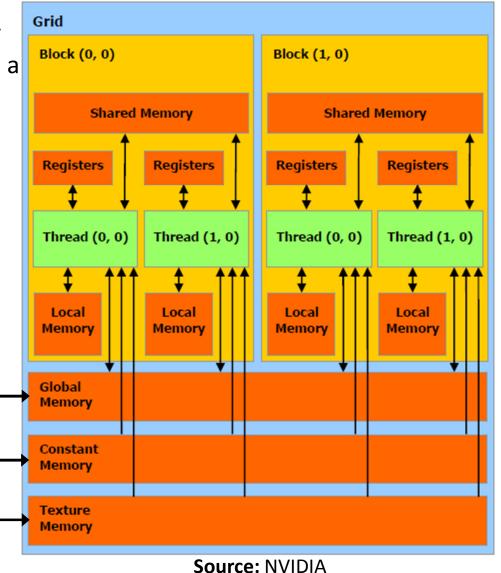

## **CUDA Memory Model**

Grid

Block (0, 0)

**Shared Memory**

#### Registers

- Very large number of registers per processor (thread)

- Instant access

#### **Local Memory**

- A portion of global memory that is private to a processor (thread)

- Used for register spills

- Slow ( same as global memory )

#### **Shared Memory**

A small (e.g., 16 KB)

block of memory

shared by all processors

(threads) in a multi

-processor (block)

Divided into Several memory banks

As fast as registers w/o bank conflicts

Source: NVIDIA

Block (1, 0)

**Shared Memory**

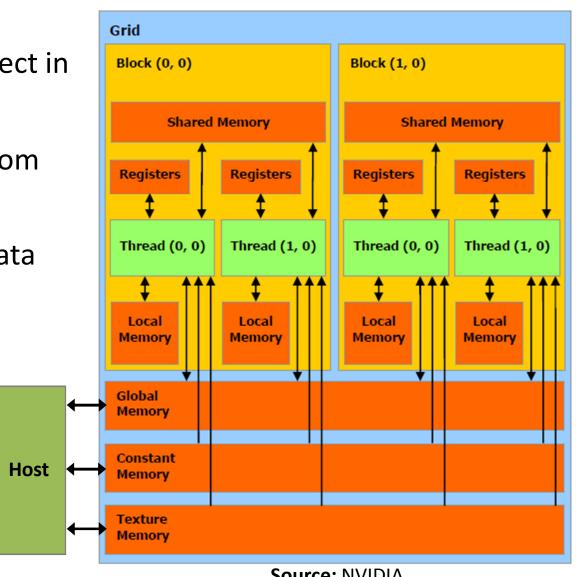

#### **CUDA Memory Model**

#### **Global Memory**

- A large block (in GB) of memory shared by all multiprocessors on a GPU

- High bandwidth ( > 100 GB/s )

- Slow ( several 100 clock cycles when not cached )

#### **Constant Memory**

- Small (e.g., 64 KB) read-only memory shared by all multiprocessors

- Cached ( per multi -processor )

- Slow ( several 100 clock cycles on cache miss )

#### **Texture Memory**

- Similar to constant memory

- Reads can be samplings (e.g., nearest point of interpolation)

Host

#### **CUDA Memory Model**

cudaMalloc(): allocates object in the devices global memory.

cudaFree( ): frees objects from device global memory.

cudaMemcpy( ): memory data transfer:

- host to host

- host to device

- device to host

- device to device

## **Synchronization**

For the following tasks control is returned to the host before the device completes the task

- Kernel launches

- Memory copies between two addresses on the same device

- Memory copies of size 64KB or less from host to device

- Memory copies by functions suffixed with Async

- Memory set function calls

However, kernel launches and cudaMemcpy can start only after all previous CUDA calls have completed.

**cudaDeviceSynchronize():** blocks until the device has completed all previously requested tasks

\_\_syncthreads(): synchronize all threads in a block

# Source: NVIDIA

#### **Example: CUDA Memory Functions**

```

// Device code

global void VecAdd(float* A, float* B, float* C, int N)

int i = blockDim.x * blockIdx.x + threadIdx.x;

if (i < N)

C[i] = A[i] + B[i];

// Host code

int main()

int N = \dots;

size t size = N * sizeof(float);

// Allocate input vectors h A and h B in host memory

float* h A = (float*)malloc(size);

float* h B = (float*)malloc(size);

// Initialize input vectors

// Allocate vectors in device memory

float* d A;

cudaMalloc(&d A, size);

float* d B;

cudaMalloc(&d B, size);

float* d C;

cudaMalloc(&d C, size);

// Copy vectors from host memory to device memory

cudaMemcpy(d A, h A, size, cudaMemcpyHostToDevice);

cudaMemcpy(d B, h B, size, cudaMemcpyHostToDevice);

// Invoke kernel

int threadsPerBlock = 256;

int blocksPerGrid =

(N + threadsPerBlock - 1) / threadsPerBlock;

VecAdd<<<br/>blocksPerGrid, threadsPerBlock>>>(d A, d B, d C, N);

// Copy result from device memory to host memory

// h C contains the result in host memory

cudaMemcpy(h C, d C, size, cudaMemcpyDeviceToHost);

// Free device memory

cudaFree(d A);

cudaFree(d B);

cudaFree(d C);

// Free host memory

```

# **CUDA Variable Type Qualifiers**

|                                       | Memory   | Scope  | Lifetime    |

|---------------------------------------|----------|--------|-------------|

| automatic variables other than arrays | register | thread | kernel      |

| automatic array variables             | local    | thread | kernel      |

| device                                | global   | grid   | application |

| shared                                | shared   | block  | kernel      |

| constant                              | constant | grid   | application |

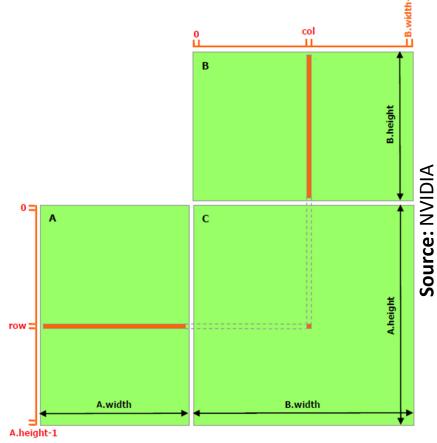

#### Matrix Multiplication w/o Shared Memory

```

// Matrices are stored in row-major order:

// M(row, col) = *(M.elements + row * M.width + col)

typedef struct {

int width;

int height;

float* elements:

// Thread block size

#define BLOCK SIZE 16

// Forward declaration of the matrix multiplication kernel

global void MatMulKernel(const Matrix, const Matrix, Matrix);

// Matrix multiplication - Host code

// Matrix dimensions are assumed to be multiples of BLOCK SIZE

void MatMul(const Matrix A, const Matrix B, Matrix C)

// Load A and B to device memory

Matrix d A:

d A.width = A.width; d A.height = A.height;

size t size = A.width * A.height * sizeof(float);

cudaMalloc(&d A.elements, size);

cudaMemcpy(d A.elements, A.elements, size,

cudaMemcpvHostToDevice);

Matrix d B;

d B.width = B.width; d B.height = B.height;

size = B.width * B.height * sizeof(float);

cudaMalloc(&d B.elements, size);

cudaMemcpy(d B.elements, B.elements, size,

cudaMemcpyHostToDevice);

// Allocate C in device memory

Matrix d C;

d C.width = C.width; d C.height = C.height;

size = C.width * C.height * sizeof(float);

cudaMalloc(&d C.elements, size);

// Invoke kernel

dim3 dimBlock(BLOCK SIZE, BLOCK SIZE);

dim3 dimGrid(B.width / dimBlock.x, A.height / dimBlock.y);

MatMulKernel <<< dimGrid, dimBlock>>> (d A, d B, d C);

// Read C from device memory

cudaMemcpy (C.elements, Cd.elements, size,

cudaMemcpyDeviceToHost);

// Free device memory

cudaFree(d A.elements);

cudaFree(d B.elements);

cudaFree (d C.elements);

```

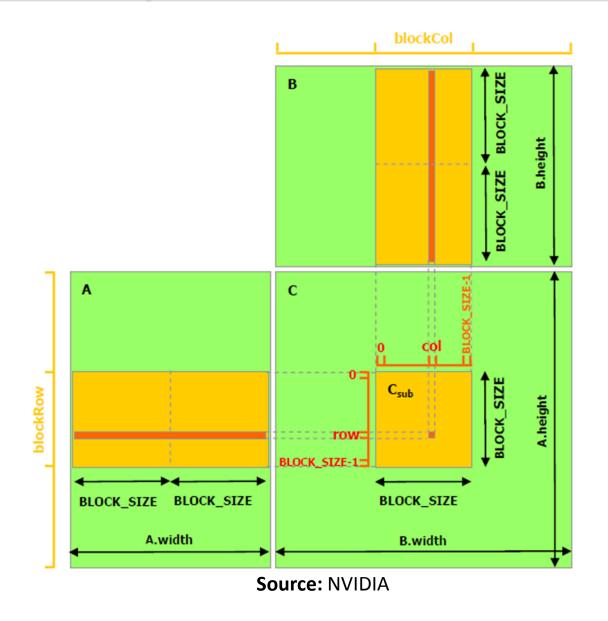

# **Matrix Multiplication with Shared Memory**

#### Matrix Multiplication with Shared Memory

```

// Matrices are stored in row-major order:

// M(row, col) = *(M.elements + row * M.stride + col)

typedef struct {

int width;

int height;

int stride;

float* elements;

Matrix;

// Get a matrix element

device float GetElement (const Matrix A, int row, int col)

return A.elements[row * A.stride + col];

// Set a matrix element

device void SetElement (Matrix A, int row, int col,

float value)

A.elements[row * A.stride + col] = value;

// Get the BLOCK SIZExBLOCK SIZE sub-matrix Asub of A that is

// located col sub-matrices to the right and row sub-matrices down

// from the upper-left corner of A

device Matrix GetSubMatrix (Matrix A, int row, int col)

Matrix Asub;

Asub.width = BLOCK SIZE;

Asub.height = BLOCK SIZE;

Asub.stride = A.stride;

Asub.elements = &A.elements[A.stride * BLOCK SIZE * row

+ BLOCK SIZE * col];

return Asub;

```

```

// Thread block size

#define BLOCK SIZE 16

// Forward declaration of the matrix multiplication kernel

global void MatMulKernel(const Matrix, const Matrix, Matrix);

// Matrix multiplication - Host code

// Matrix dimensions are assumed to be multiples of BLOCK SIZE

void MatMul(const Matrix A, const Matrix B, Matrix C)

// Load A and B to device memory

Matrix d A;

d A.width = d A.stride = A.width; d A.height = A.height;

size t size = A.width * A.height * sizeof(float);

cudaMalloc(&d A.elements, size);

cudaMemcpy(d A.elements, A.elements, size,

cudaMemcpyHostToDevice);

Matrix d B;

d B.width = d B.stride = B.width; d B.height = B.height;

size = B.width * B.height * sizeof(float);

cudaMalloc(&d B.elements, size);

cudaMemcpy(d B.elements, B.elements, size,

cudaMemcpyHostToDevice);

// Allocate C in device memory

Matrix d C;

d C.width = d C.stride = C.width; d C.height = C.height;

size = C.width * C.height * sizeof(float);

cudaMalloc(&d C.elements, size);

// Invoke kernel

dim3 dimBlock (BLOCK SIZE, BLOCK SIZE);

dim3 dimGrid(B.width / dimBlock.x, A.height / dimBlock.y);

MatMulKernel <<< dimGrid, dimBlock>>> (d A, d B, d C);

```

#### Matrix Multiplication with Shared Memory

```

// Read C from device memory

cudaMemcpy(C.elements, d C.elements, size,

cudaMemcpyDeviceToHost);

// Free device memory

cudaFree(d A.elements);

cudaFree(d B.elements);

cudaFree(d C.elements);

// Matrix multiplication kernel called by MatMul()

global void MatMulKernel (Matrix A, Matrix B, Matrix C)

// Block row and column

int blockRow = blockIdx.y;

int blockCol = blockIdx.x;

// Each thread block computes one sub-matrix Csub of C

Matrix Csub = GetSubMatrix(C, blockRow, blockCol);

// Each thread computes one element of Csub

// by accumulating results into Cvalue

float Cvalue = 0;

// Thread row and column within Csub

int row = threadIdx.v;

int col = threadIdx.x;

// Loop over all the sub-matrices of A and B that are

// required to compute Csub

// Multiply each pair of sub-matrices together

// and accumulate the results

for (int m = 0; m < (A.width / BLOCK SIZE); ++m) {</pre>

// Get sub-matrix Asub of A

Matrix Asub = GetSubMatrix(A, blockRow, m);

```

```

// Get sub-matrix Bsub of B

Matrix Bsub = GetSubMatrix(B, m, blockCol);

// Shared memory used to store Asub and Bsub respectively

shared float As[BLOCK SIZE] [BLOCK SIZE];

shared float Bs[BLOCK SIZE][BLOCK SIZE];

// Load Asub and Bsub from device memory to shared memory

// Each thread loads one element of each sub-matrix

As[row][col] = GetElement(Asub, row, col);

Bs[row][col] = GetElement(Bsub, row, col);

// Synchronize to make sure the sub-matrices are loaded

// before starting the computation

syncthreads();

// Multiply Asub and Bsub together

for (int e = 0; e < BLOCK SIZE; ++e)</pre>

Cvalue += As[row][e] * Bs[e][col];

// Synchronize to make sure that the preceding

// computation is done before loading two new

// sub-matrices of A and B in the next iteration

syncthreads();

// Write Csub to device memory

// Each thread writes one element

SetElement (Csub, row, col, Cvalue);

```

#### **Some Optimization Tips**

- Increase data parallelism

- Keep resource usage (e.g., registers, shared memory) low enough to allow multiple warps per multiprocessor

- Increase arithmetic intensity

- Recompute on device to avoid costly host to device data transfers

- Use the fast shared memory more than the slow global memory

- Increase coalesced accesses to global memory

- Avoid bank conflicts in shared memory

- Improve spatial locality for cached memory

- One large data transfer is much faster than many small transfers